# UNIVERSIDADE FEDERAL DO CEARÁ CENTRO DE TECNOLOGIA DEPARTAMENTO DE ENGENHARIA ELÉTRICA PROGRAMA DE PÓS-GRADUAÇÃO EM ENGENHARIA ELÉTRICA

#### DALTON DE ARAÚJO HONÓRIO

### AN INTERLEAVED-STAGE AC-DC CONVERTER FEASIBLE FOR SST-BASED RAILWAY TRACTION SYSTEMS

FORTALEZA 2018

#### DALTON DE ARAÚJO HONÓRIO

### AN INTERLEAVED-STAGE AC-DC CONVERTER FEASIBLE FOR SST-BASED RAILWAY TRACTION SYSTEMS

Tese apresentada ao Programa de Pósgraduação em Engenharia Elétrica da Universidade Federal do Ceará, como requisito parcial à obtenção do título de Doutor em Engenharia Elétrica. Área de concentração: Sistema de Energia Elétrica.

Orientador: Prof. Dr. Luiz Henrique Silva Colado Barreto.

Coorientador: Prof. Dr. Demercil de Souza Oliveira Júnior.

**FORTALEZA**

## Dados Internacionais de Catalogação na Publicação Universidade Federal do Ceará Biblioteca Universitária Gerada automaticamente pelo módulo Catalog, mediante os dados fornecidos pelo(a) autor(a)

#### H749a Honório, Dalton de Araújo.

An Interleaced-stage ac-dc converter feaseble for sst-based railway traction systems / Dalton de Araújo Honório. -2018.

94 f.: il. color.

Tese (doutorado) – Universidade Federal do Ceará, Centro de Tecnologia, Programa de Pós-Graduação em Engenharia Elétrica, Fortaleza, 2018.

Orientação: Prof. Dr. Luiz Henrique Silva Colado Barreto.

Coorientação: Prof. Dr. Demercil de Souza Oliveira Júnior.

1. transformador de estado sólido. 2. conversor modular bidirecional. 3. correção do fator de potência. 4. modulação vetorial. I. Título.

CDD 621.3

#### DALTON DE ARAÚJO HONÓRIO

### AN INTERLEAVED-STAGE AC-DC CONVERTER FEASIBLE FOR SST-BASED RAILWAY TRACTION SYSTEMS

Thesis presented to the Doctoral Course in Electrical Engineering of the Electrical Engineering Department of Federal University of Ceará as part of the requirements for obtaining the title of Doctor of Philosophy (Ph.D.) in Electrical Engineering. Concentration Area: Electric Power Systems.

Approved in: 23/02/2018

#### **EXAMINATION BOARD**

| Prof. | Dr. Luiz Henrique Silva Colado Barreto (Advisor)<br>Universidade Federal do Ceará (UFC)   |

|-------|-------------------------------------------------------------------------------------------|

| Prof. | Dr. Demercil de Souza Oliveira Júnior (Co-advisor)<br>Universidade Federal do Ceará (UFC) |

|       | Prof. Dr. Yales Rômulo de Novaes<br>Universidade do Estado de Santa Catarina (UDESC)      |

|       | Prof. Dr. Rafael Rocha Matias<br>Universidade Federal do Piauí (UFPI)                     |

|       | Dr. Burak Ozpineci<br>Oak Ridge National Laboratory (ORNL)                                |

|       | Prof. Dr. Paulo Peixoto Praça Universidade Federal do Ceará (UFC)                         |

#### **RESUMO**

Esse trabalho propõe um conversor de potência com estágio intercalado CA-CC com características bidirecionais factível para aplicações de sistemas de ferrovia em média tensão. Ele é baseado em um arranjo que conecta os terminais de entrada em série e de os de saída em paralelo com módulos de potência idênticos. Existem dois tipos de módulos: o Tipo A consiste em dois braços intercalados empregando enrolamento acoplados de tal forma que seja possível a conexão de um transformador operando em média frequência, aliado a um célula dobradora de tensão, enquanto Tipo B também utiliza braços intercalados, contudo com um braço adicional operando na frequência da rede, substituindo a célula dobradora. A concepção da topologia é apresentada, seguida pela estratégia de controle adotada, bem como da modulação empregada. Uma estimação das perdas nos semicondutores é também discutida através de uma análise comparativa utilizando resultados de simulação, validando o desempenho superior da topologia proposta frente a soluções similares. Os resultados da topologia são obtidos através de testes experimentais em dois protótipos da topologia proposta considerando módulos do Tipo A. A estrutura de um único módulo demonstra as funcionalidades de comportamentos do conversor sobre as condições de regime permanente e transitórios, enquanto o protótipo com dois módulos demonstra as mesmas características em uma estrutura com múltiplos módulos. Com isso, é possível atestar o bom comportamento em termos de eficiência, mesmo o conversor proposto apresentando um número maior de componente magnéticos se comparado com soluções similares. Assim, a solução proposta é adequada para aplicações de alto níveis de potência em sistemas de acionamentos de máquinas de estágio CA-CC.

**Palavras-chave**: Transformador de estado sólido. Conversor modular bidirecional. Correção do fator de potência. Modulação vetorial.

#### **ABSTRACT**

This work proposes an interleaved-stage ac-dc bidirectional power converter topology feasible to medium-voltage (MV) railway systems. It is based on an arrangement that uses Input-Series-Output-Parallel (ISOP) configuration with identical power modules. There are two types of modules: Type A consists of two interleaved legs employing coupled-windings so that it is possible to connect a medium-frequency transformer (MFT), together with a voltage doubler cell, while Type B also uses the two interleaved legs, however with an additional one operating in the grid frequency in order to replace the voltage doubler cell. The topology conception is presented, followed by the adopted control and modulation technique. An estimation of semiconductor losses is also discussed through a comparative analysis by means of simulation results, validating the improved performance of the introduced approach if compared with similar solutions. The topology results are obtained through experimental test performed in two prototypes of the proposed topology, considering module type A. The single-module demonstrates the converter functionalities and performance under both steady-state and dynamic conditions, while the two-module structure demonstrates the same aspects for multimodule configurations. It is then possible to state that good performance in terms of efficiency even though the proposed power converter presents higher magnetic component count if compared with similar topology, thus making it suitable to high-power AC-DC machine drive applications.

**Keywords**: Solid state transformer. Modular directional converter. Power factor correction. Space vector modulation.

#### LIST OF FIGURES

| Figure 1.1 – Power electronic converters used in traction applications: (a) Classical approach                         |

|------------------------------------------------------------------------------------------------------------------------|

| with LFT, (b) SST-based approach with MFT1                                                                             |

| Figure 1.2 – Generic SST configuration1                                                                                |

| Figure 1.3 – SSTs power stage categorization                                                                           |

| Figure 1.4 – Publication statistic of SST-based railway traction application                                           |

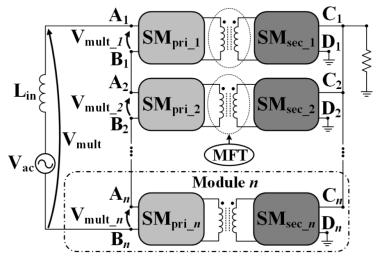

| Figure 2.1 – Generalized structure of the proposed topology                                                            |

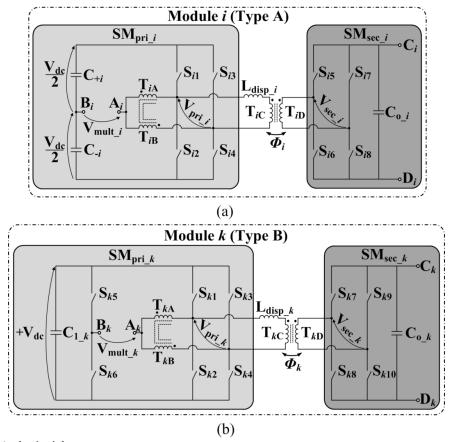

| Figure 2.2 – The inner configuration of the module: (a) power module type A, (b) power module                          |

| type B2                                                                                                                |

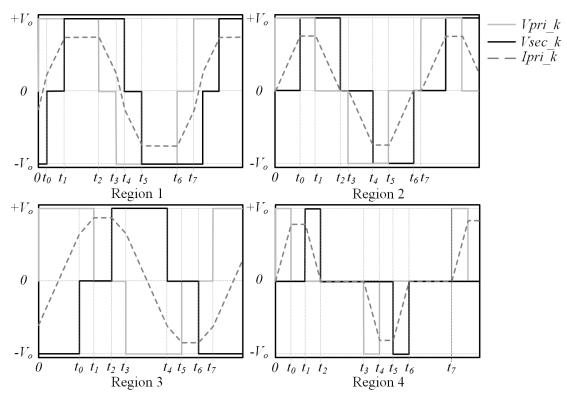

| Figure 2.3 – Type A operational aspects: (a) main theoretical waveforms during a switchin period, (b) Operation stages |

|                                                                                                                        |

| Figure 2.4 – Type B operational aspects: (a) main theoretical waveforms during a switchin period, (b) Operation stages |

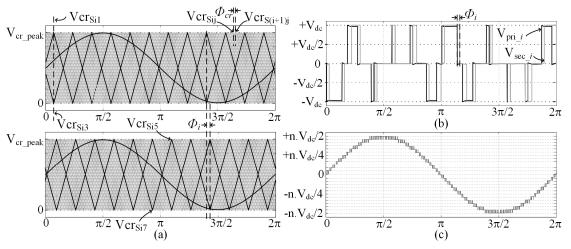

| Figure 2.5 – Carrier-based adopted modulation for type A module: (a) carriers dispositions for                         |

| twelve-module converter configuration, (b) voltage waveforms in $V_{pri\_i}$ and $V_{sec}$                             |

| with the phase shift of $\Phi_i$ , (c) voltage levels in Vmult using the modulation                                    |

| technique and nmin(A)=12                                                                                               |

| Figure 2.6 - Carrier-based adopted modulation for type B module: (a) singular modulating                               |

| waveform produced by (2.5), (b) modulating waveform produced by ne                                                     |

| modulation arrangement, (c) proposed comparison and combinational stages of                                            |

| the new modulation arrangement                                                                                         |

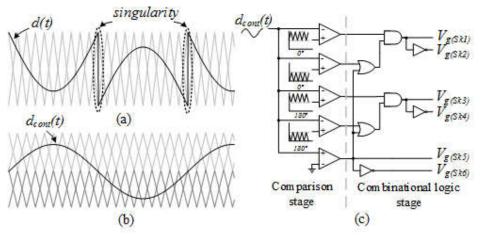

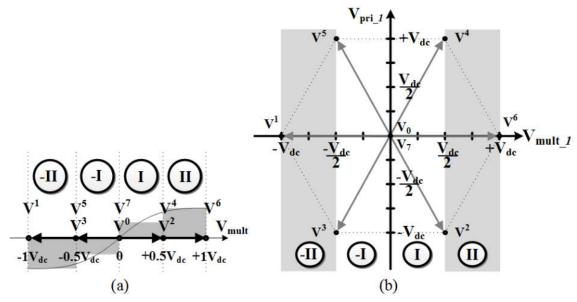

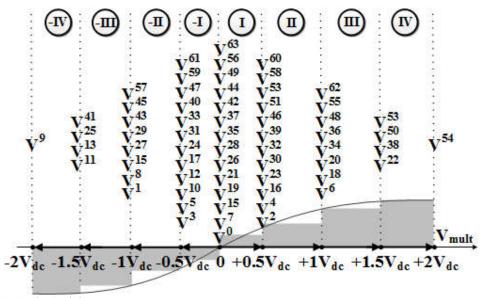

| Figure 2.7 – Figure of merit of the proposed SVM: (a) space diagram of the multilevel voltage                          |

| across the converter; (b) space diagram of the multilevel voltage versus the MF                                        |

| primary voltage                                                                                                        |

| Figure 2.8 – Proposed switching sequence for the single-module topology with type B module                             |

| Figure 2.0 CGVGil                                                                                                      |

| Figure 2.9 – SSVS considering the two-module configuration of the proposed converter, using                            |

| modules type B                                                                                                         |

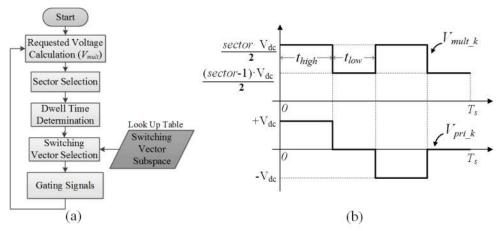

| Figure 2.10 – Figure of merit of the proposed SVM: (a) low chart for the proposed space vector                         |

| modulation algorithm; (b) determination of the dwell time in the propose                                               |

| algorithm                                                                                                              |

| Figure 2.11 – Control block diagram applied to the proposed topology: (a) considering type                             |

| modules; (b) considering type B modules                                                                                |

| Figure 2.12 – q-PLL structure applied in the control methodology                                                       |

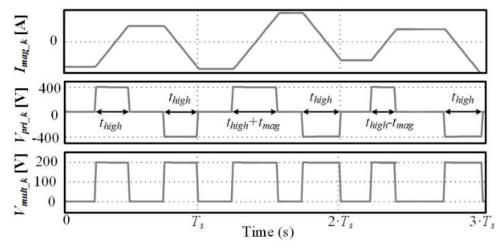

| Figure 2.13 – Magnetizing current behavior with the magnetizing control loop                 | 42     |

|----------------------------------------------------------------------------------------------|--------|

| Figure 2.14 – Model adopted to the input inductance filter analysis                          | 43     |

| Figure 2.15 – Operation regions of the proposed converter considering type B modules         | 44     |

| Figure 2.16 – Boundary conditions for region and duty cycle functions                        | 48     |

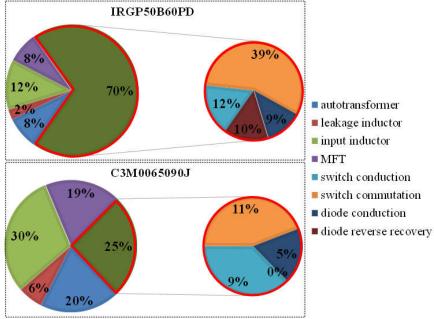

| Figure 2.17 – Proposed converter losses distribution                                         | 54     |

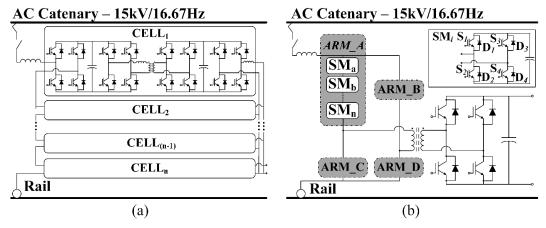

| Figure 2.18 – Generalized structure of ac-dc/dc-dc and ac-dc SSTs: (a) PET with AFE topol    | ogy,   |

| (b) M <sup>2</sup> LC Topology                                                               | 55     |

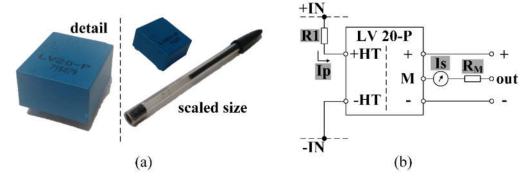

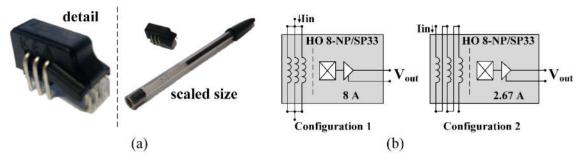

| Figure 3.1 – Isolated voltage sensor: (a) physic aspect, (b) recommended circuit connect     | ions   |

|                                                                                              | 60     |

| Figure 3.2 – Isolated current sensor: (a) physic aspect, (b) recommended circuit connect     | ions   |

|                                                                                              | 61     |

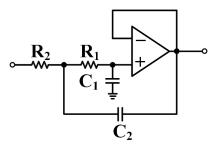

| Figure 3.3 – Second order Butterworth filter circuit                                         | 62     |

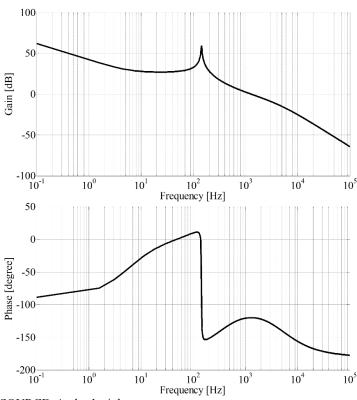

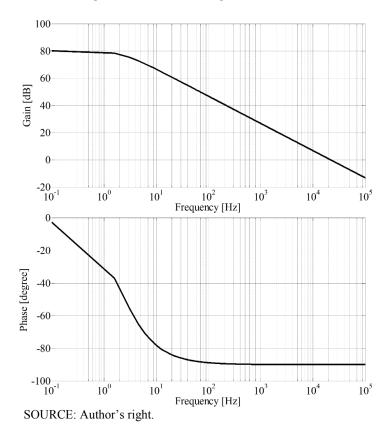

| Figure 3.4 – Bode diagram of OLTFv                                                           | 63     |

| Figure 3.5 – Bode diagram of OLTFv compensated                                               | 66     |

| Figure 3.6 – Bode diagram of OLTFi                                                           | 67     |

| Figure 3.7 – Bode diagram of OLTFi compensated                                               | 68     |

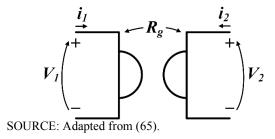

| Figure 3.8 – Proposed symbol for the ideal gyrator                                           | 69     |

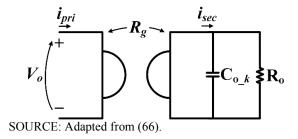

| Figure 3.9 – Equivalent circuit of the load port                                             | 69     |

| Figure 3.10 – Bode diagram of OLTFvout                                                       | 70     |

| Figure 3.11 – Bode diagram of FTLAvout compensated                                           | 71     |

| Figure 3.12 – Bode diagram of OLTFvdc_banl compensated                                       | 72     |

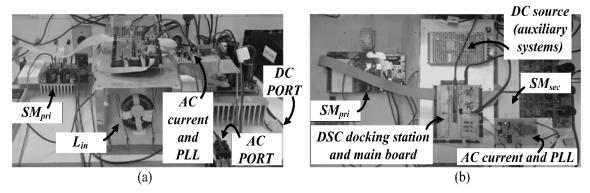

| Figure 4.1 – Single-module structure prototype: (a) front view, (a) superior view            | 74     |

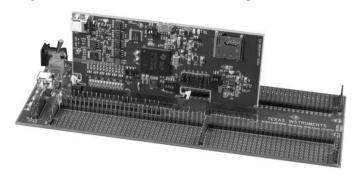

| Figure 4.2 – TMDSDOCK28377D Experimenter's kit                                               | 75     |

| Figure 4.3 – Two-module structure prototype                                                  | 75     |

| Figure 4.4 – Single-module structure steady-state behavior for the input voltage and current | t: (a) |

| simulation results, (b) experimental results                                                 | 77     |

| Figure 4.5 - Single-module structure steady-state behavior for the multilevel voltage.       | (a)    |

| simulation results, (b) experimental results                                                 | 77     |

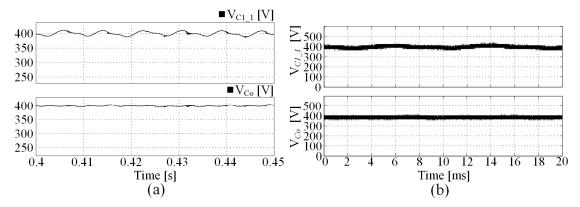

| Figure 4.6 - Single-module structure steady-state behavior for the voltages across capa      | citor  |

| $C_{I_{\_}I}$ and $C_o$ : (a) simulation results, (b) experimental results                   | 78     |

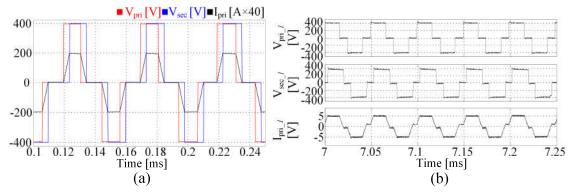

| Figure 4.7 – Single-module structure steady-state behavior for the voltages across the MFT   | and    |

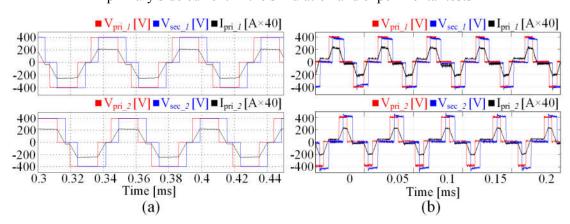

| the current, as well: (a) simulation results, (b) experimental results                       | 78     |

| Figure 4.8 - Two-module structure steady-state behavior for the ac current in the induce     | ctive  |

| filter: (a) simulation results, (b) experimental results                                     | 80     |

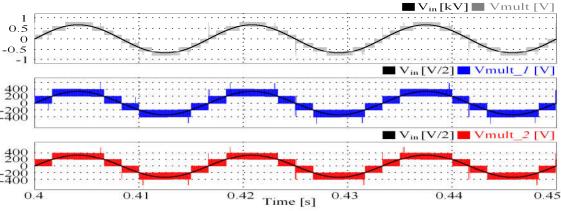

| Figure 4.9 – Two-module structure steady-state behavior for the multilevel voltages in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | the  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| simulation model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 80 |

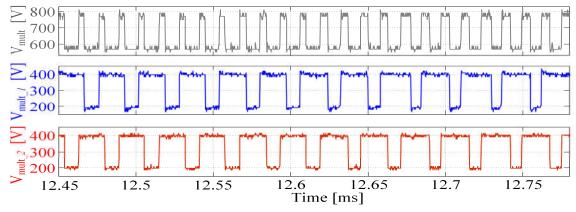

| Figure 4.10 - Two-module structure steady-state behavior for the multilevel voltages in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | the  |

| experimental test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 81 |

| Figure 4.11 – Detailed two-module structure steady-state behavior for the multilevel voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | s in |

| the experimental test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 81 |

| Figure 4.12 - Two-module structure steady-state behavior for the dc voltages in the simular                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | tion |

| and experimental tests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 82 |

| Figure 4.13 – Two-module structure steady-state behavior for the MFT voltages and its primare the structure steady-state behavior for the MFT voltages and its primare steady-state behavior for the MFT voltages and its primare steady-state behavior for the MFT voltages and its primare steady-state behavior for the MFT voltages and its primare steady-state behavior for the MFT voltages and its primare steady-state behavior for the MFT voltages and its primare steady-state behavior for the MFT voltages and its primare steady-state behavior for the MFT voltages and its primare steady-state behavior for the MFT voltages and its primare steady-state behavior for the MFT voltages and its primare steady-state behavior for the MFT voltages and its primare steady-state behavior for the MFT voltages and its primare steady-state behavior for the MFT voltages and its primare steady-state behavior for the MFT voltages and its primare steady-state behavior for the MFT voltages and the state of the meaning steady-state behavior for the MFT voltages and the state of the meaning steady-state steady | ıary |

| side current in the simulation and experimental tests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 82 |

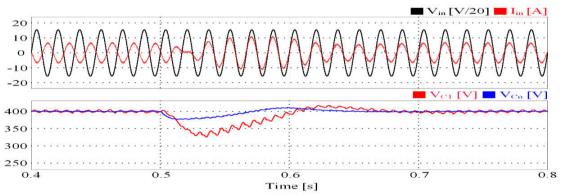

| Figure 4.14 – Single-module structure dynamic behavior for the reversion power flow test in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | the  |

| simulation model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 83 |

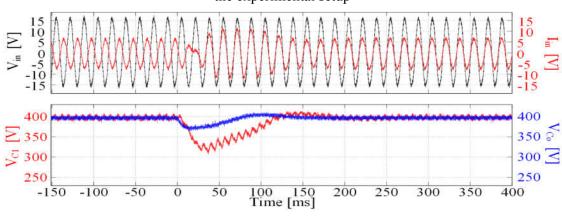

| Figure 4.15 – Single-module structure dynamic behavior for the reversion power flow test in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | the  |

| experimental setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 84 |

| Figure 4.16 - Two-module structure dynamic behavior for reversion power flow test in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | the  |

| simulation model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 84 |

| Figure 4.17 - Two-module structure dynamic behavior for reversion power flow test in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | the  |

| experimental setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 85 |

#### LIST OF GRAPHS

| Graph 1.1 – Number of scientific papers published by IEEE, related to S     | SST-based railway  |

|-----------------------------------------------------------------------------|--------------------|

| traction application, in the last decade                                    | 15                 |

| Graph 4.1 – Single-module experimental efficiency: (a) rectification mode ( | (b) inversion mode |

|                                                                             | 79                 |

#### LIST OF TABLES

| Table 1.1– Comparison between SST-based and LFT-based applications          | 20           |

|-----------------------------------------------------------------------------|--------------|

| Table 2.1– Switching states for a single-module structure                   | 35           |

| Table 2.2– Instants considered in each operating region                     | 44           |

| Table 2.3– MFT primary voltage by Region                                    | 45           |

| Table 2.4– Currents expression for Region 1 and 2                           | 45           |

| Table 2.5– Currents expression for Region 3 and 4                           | 46           |

| Table 2.6– Instantaneous power expression by Region                         | 46           |

| Table 2.7– Quasi-instantaneous Power by Region                              | 47           |

| Table 2.8– Boundary instants by its transition of regions                   | 48           |

| Table 2.9– Electric characteristics of the switch used in the analyses      | 51           |

| Table 2.10– Switches losses                                                 | 52           |

| Table 2.11– Converter specifications                                        | 52           |

| Table 2.12– Inductor characteristics                                        | 53           |

| Table 2.13– Transformers characteristics                                    | 53           |

| Table 2.14– Magnetics losses                                                | 53           |

| Table 2.15– Design parameters considered in the comparative losses analysis | 55           |

| Table 2.16– Comparison result of the typical railway systems topologies     | 56           |

| Table 3.1– Design parameters and specifications                             | 59           |

| Table 3.2– Parameterization of the applied voltages sensors                 | 60           |

| Table 3.3– Parameterization of the applied filters                          | 62           |

| Table 3.4– Parameters of the dc link voltage controller                     | 65           |

| Table 3.5– Parameters of the input current controller                       | 68           |

| Table 3.6– Parameters of the output voltage controller                      | 71           |

| Table 3.7– Parameters of the dc link balancing voltage controller           | 73           |

| Table 4.1-Mainly devices applied in the experimental setup, considering the | e two-module |

| configuration                                                               | 76           |

#### LIST OF CONTENTS

| 1       | INTRODUCTION                                                   | 13 |

|---------|----------------------------------------------------------------|----|

| 1.1     | Thesis contextualization and motivation                        | 13 |

| 1.2     | Background of SST applied in traction systems                  | 15 |

| 1.2.1   | SSTs concepts and classification                               | 15 |

| 1.2.2   | Requirements and aspects of a railway traction system          | 18 |

| 1.2.3   | Comparison between SST-based and classical LFT-based solutions | 19 |

| 1.2.4   | State-of-the-art of SST-based railway traction solutions       | 20 |

| 1.3     | Objectives and expected contributions                          | 23 |

| 1.4     | Thesis outline                                                 | 23 |

| 2       | PROPOSED TOPOLOGY                                              | 25 |

| 2.1     | Qualitative analysis                                           | 25 |

| 2.1.1   | Conception                                                     | 25 |

| 2.1.2   | Operation                                                      | 27 |

| 2.1.2.1 | Type A                                                         | 28 |

| 2.1.2.2 | Type B                                                         | 29 |

| 2.1.3   | Modulation technique                                           | 31 |

| 2.1.3.1 | Carrier-Based Modulation                                       | 31 |

| 2.1.3.2 | Space Vector Modulation                                        | 34 |

| 2.1.4   | Control system                                                 | 39 |

| 2.2     | Quantitative analysis                                          | 42 |

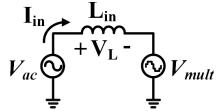

| 2.2.1   | Input Inductance determination                                 | 43 |

| 2.2.2   | Complete model                                                 | 43 |

| 2.2.3   | Analysis of losses                                             | 49 |

| 2.2.3.1 | Conduction and switching losses calculation                    | 50 |

| 2.2.3.2 | Transformer and inductance losses calculation                  | 52 |

| 2.2.3.3 | Converter efficiency                                           | 54 |

| 2.2.3.4 | Comparative losses analysis                                    | 54 |

| 3       | DESING PROCEDURE                                               | 59 |

| 3.1     | Sensors                                                        | 59 |

| 3.1.1   | Voltage                                                        | 59 |

| 3.1.2   | Current                                                        | 61 |

| 3.2     | Anti-aliasing filter                                           | 61 |

| 3.3     | Controllers designs                     | 62 |

|---------|-----------------------------------------|----|

| 3.3.1   | Voltage DC link controller              | 62 |

| 3.3.2   | Input current controller                | 66 |

| 3.3.3   | Output voltage controller               | 69 |

| 3.3.4   | DC link voltage balancing controller    |    |

| 4       | EXPERIMENTAL SETUP AND RESULTS          | 74 |

| 4.1     | Prototypes description                  | 74 |

| 4.2     | Simulation and experimental results     | 76 |

| 4.2.1   | Steady-state behavior                   |    |

| 4.2.1.1 | Single-module power converter structure | 76 |

| 4.2.1.2 | Two-module power converter structure    | 79 |

| 4.3     | Dynamic behavior                        | 83 |

| 4.3.1.1 | Single-module power converter structure | 83 |

| 4.3.1.2 | Tow-module power converter structure    | 84 |

| 5       | CONCLUSION                              | 86 |

| 5.1     | Scientific Production                   | 87 |

| 5.1.1   | Proceeding Papers                       | 87 |

| 5.1.2   | Journal Papers                          | 88 |

|         | BIBLIOGRAPHY                            | 89 |

#### 1 INTRODUCTION

#### 1.1 Thesis contextualization and motivation

Since its initial conception, the transformer has been used in the most diverse applications where insulation and adaptation of voltage levels are demanded. In fact, this device is widely employed either directly or indirectly in all electrical engineering fields due its simple design for distinct power and voltage conversion levels. In order to evidence how near this technology is from us, the reader, very likely, is using an electronic device with transformer in some part of its circuits to access this document, or it was used an electronic printer, which, also, applies transformer in some part of its inner electronics circuits, to obtain the paper based version of this document.

Transformers are the simplest magnetics circuits which can provide coupling with one or more electric circuits and their designs suffer minor changes as both power and voltage levels are varied. They are used in plenty kind of electric systems providing, impedance matching between the source and the load, filtering the dc current component on an ac power supply, and the aforementioned characteristics: galvanic insulation and voltage levels adaptation (1).

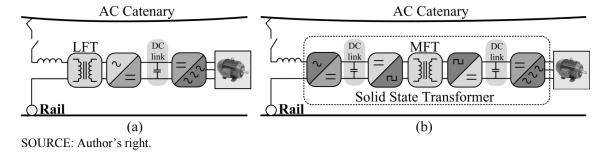

More specifically, the power transformer ensures such characteristics in power systems applications, such as: ac power energy transmission and distribution, as well as, medium-voltage machine drives. However, these applications are typically based on a bulky low-frequency device called Line Frequency Transformer (LFT) (2), as presented in Figure 1.1a.

Figure 1.1 – Power electronic converters used in traction applications: (a) Classical approach with LFT, (b) SST-based approach with MFT

The size, weight and volume of these devices are closely related to the respective operating frequency, whose decrease causes the very augmentation of the magnetic (3). Moreover, if it is necessary to deal with power quality issues, such as voltages sags, flicker, harmonics and others, the inclusion of external devices are necessary to provide proper

protection, increasing the global volume of the transformer even further. Besides, many applications normally use oil inside the transformer for cooling and insulation purposes, what has direct impact on weight and volume and implies serious environmental issues (4). It is worth to mentioned, though, that in traction application normally the LFT are dry or oil less. On the other hand, the efficiency of the LFTs in this applications is low, since they are typically designed with high current densities (as less amount of copper is required) and efficiency range about (90-95)% (5). As a result, the use of the classical power transformer can become a limiter or even unfeasible in some applications such as traction and naval transportations (6).

In order to address a lighter transformer for such applications, the first concept involving this matter is to replace the conventional bulky transformer operating at the line (catenary) frequency, which is usually lower than 100 Hz (7), by a solution using a transformer designed for an operating frequency around thousands of hertz. Such reduction is a must in medium-voltage machine drives, more particularly in electric railway application, since a more compact propulsion system is a requirement, resulting in the improvement of the transformer design and reduction of the requested power with the same cargo capability. This advantage is specially desired in Electric Multiple Units (EMU) where the propulsion system is distributed among the locomotive's cars (8).

Nowadays, with the power electronics development, trend applications accomplish such transformer replacement by applying power converter topologies with medium-frequency transformers (MFTs), these solutions are denominated as Solid State Transformer (SST), as presented in Figure 1.1b. Then, the classical LFT is no longer the only answer, when high-voltage, high-power capabilities are required in traction systems (9).

In fact, since the past decade both academic and the industry communities are spending research efforts in SST in the most diverse power electronic areas. Such interest can be note by looking the Figure 1.1, where it shown the SST-based railway systems publication statistic for the last decade. The focus of these studies are spread in several branches of railway traction applications, providing key concepts, new SST topologies, MFT analysis and design improvements, viability analysis of real scenarios and related subjects (10).

Hence, all the presented information and the recently attention around the SST applications (more specifically in traction systems) drive and motivate this PhD research and consequently this thesis.

19 17 15 13 9 7 5 3 1 2007 2008 2009 2010 2011 2012 2013 2014 2015 2016 2017 Year of publication

Graph 1.1 – Number of scientific papers published by IEEE, related to SST-based railway traction application, in the last decade

SOURCE: Author's right.

#### 1.2 Background of SST applied in traction systems

In order to allow for a better understanding about SSTs in railway traction systems and verify their potential in this application, it is necessary to know their basic concepts, aspects, requirements and compare them with the classical LTF approaches. Moreover, each SST solution can be sorted into a pre-established category, which helps either their historical presentation, as to note the evolution in the research lines of them. Hence, this chapter presents the SST technology focused in the aforementioned branches, as well as, its state-of-the-art in railway traction systems.

#### 1.2.1 SSTs concepts and classification

As mentioned before, one possible solution to replace the LFT in power systems is to apply MFT together with power electronics structures. The general goal of the SST is to adapt the high-voltage level, in the targeted power application, for medium- or low-voltage levels, increasing dramatically its compatibility. Figure 1.2 presents a generic configuration of the SST concept.

It is possible to note from Figure 1.2 that the voltage level in the power source is used by the first power converter in order to modulate a voltage with medium frequency spectrum in the terminals of the MFT. Next, such modulated voltage is stepped-down by the

MFT's turns ratio, and then it is used by the second power converter to be adapted for a more feasible one, depending on the targeted application.

Figure 1.2 – Generic SST configuration

SST

DOWED

SOURCE: Author's right.

SOURCE

The SST features can be summarized as follow.

- The transformer operates at a medium frequency, from hundreds Hertz to kilohertz;

- It is necessary application of power electronics converters, to provide medium frequency operation;

- High-voltage power devices are used in the input terminals due the grid (catenary) characteristics.

- The voltage in the MFT nominally is not sinusoidal, due the power switching structures.

The SST application creates a large number of possibilities to be explored, since a large number of power converters can be adapted or even conceived for this matter. Then, some SST classifications are demanded to sort the solutions which already exist and those which will be considered in future.

In (11), it is presented a classification in terms of power conversion stages in the SST topologies, focusing on power distribution systems. In the studies elaborated by (12) and (13), it is presented a similar classification together with other one in terms of the MFT windings configuration. Kolar and Ortiz (14) show three different forms to categorize SSTs. The first one sees the SSTs in terms of how the structure provides the power flow, while the second one is concerned in the configuration used by the SST to link three-phase systems, which is similar with the one presented by (11). At last, the third classification is focused on how the SST is supposed to connect the high-voltage grid terminals, being comparable with the one presented in (12).

In this thesis, the SST solutions will be presented considering the power conversion stages category and assuming that they must provide a dc link voltage to the machine drive

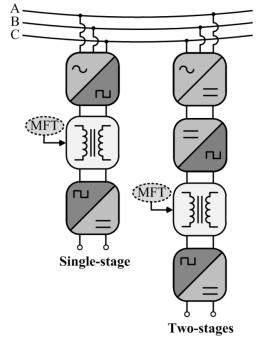

systems. Therefore, it is possible to briefly classify the main characteristics of the SST topologies in two different categories, as presented in Figure 1.3.

Figure 1.3 – SSTs power stage categorization

SOURCE: Author's right.

The definitions of the conversion stages considered in this thesis is presented as follow.

• **single-stage approaches (ac-dc):** This solution usually uses bidirectional switches to create a high-voltage connection capability at its input terminals with an isolated medium frequency link without a dc link in the primary side of the MFT. It provides a dc voltage to the locomotive's drive machine systems in the secondary side of the MFT.

To aggregate such high-voltage connection capability without the presence of a medium-voltage dc link, some works propose cycloconverters combined with a voltage-source active rectifier (15) or with bidirectional converters structures (16). A general cycloconverter consisting of individual modules is proposed in (17) to decrease the power levels associated to MFTs. However, there is appreciable reactive content through the transformer due to the low-frequency envelop of the voltage waveform across the primary side of the transformer.

• two-stages approaches (ac-dc/dc-dc): Such topologies also allow high-voltage input connection, but the additional conversion stage brings more flexibility to the whole structure. The isolated medium-frequency is commonly placed at the

dc-dc stage, since the isolated dc-dc stage is a well-known power electronic structures.

The work presented in (18) uses a cascaded high-voltage rectifier whose input voltage is rated at 7.2 kV, as well as a dual active bridge converter responsible for isolation and voltage step down from 3.8 kV to 400 V. Thus, the ac-dc converter is able to perform power factor correction, while the dc-dc stage is decoupled from the dc link (in the control aspect) and the design of the DAB converter can be optimized for a wide soft switching range. A similar topology is used in (19), but a different arrangement is proposed for the MFT, allowing multiport connections and consequently, flexibility for both EMU trains and locomotives machine drivers. The multiport connection in (20) is also used, but for power management purposes, since ports with different characteristics i.e. distributions systems, low-voltage dc storage plants, medium-voltage ac machine driver, among others are connected to provide a versatile and flexible power system.

Besides these categories, it is possible to find SST solutions which integrate two conversion stages. They use dc links to modulate the voltage across the primary side of the MFT without using an isolated dc-dc stage. In other words, the same semiconductor structure provides the dc link and the ac voltage across the MFT, instead of employing an H-bridge used as an ac-dc stage and another dc-ac one. Although such topologies could be considered as a middle term between the aforementioned categories, this work is supposed to treat them as a single-stage approach. An example for this kind of structure is the modular multilevel converter called M<sup>2</sup>LC presented in (21), which uses cascaded full bridge converters in an H-bridge arrangement i.e. a set of cascaded converters form the upper and the lower arms of the structures' legs. Hence, medium-frequency isolation can be achieved without using an additional dc-dc isolated stage and high efficiency is achieved with high power density.

#### 1.2.2 Requirements and aspects of a railway traction system

The evolution of railway traction systems is instigated by market requirements, which can be summarized by seven topics: 1) smart cargo capability use, 2) low floor accessing, 3) reliability, 4) operating life time, 5) minimized preventive maintenance, 6) motor technology improvement and 7) cost reduction on active components (22). In other words, the traction system should be attractive as much as individual transportation (cars, motorcycles, bicycles and etc.) over short distances and aircraft over long distances. To accomplish that, the on board power consumption of the trains shall increase, since air conditioning, automatic access, lights,

personal electronics devices and electronics charging stations, are becoming common in this applications (23).

Although traction systems are supposed to increase the passenger comfort, the real improvement should come from technology breakthrough in the components, more specifically in active power components (24) in the main electric power system. Then, to address the aforementioned requirements, the railway traction system should have the following aspects.

**High efficiency**: increment of the auxiliary power (on board consumption) with a slight addition of the total demanded power.

**High power density**: low weight in an elevated power level structure.

**Reliability and reduced maintenance**: constant improvement of the mean time before failure (MTBF) index.

**High-voltage singe-phase capabilities**: since the typically single-phase railway AC lines are 15 kV at  $16\frac{2}{3} \text{ Hz}$  and 25 kV at 50 Hz (5), the SST solution should deal with these magnitudes.

#### 1.2.3 Comparison between SST-based and classical LFT-based solutions

With the information presented so far about LFT-based and SST-based railway traction systems, it is possible to provide a comparison analysis between both approaches.

Besides the volume, weight and material cost reductions of the transformer in SST-based applications due the medium frequency operation, it is possible to highlight some other advantages, like the possibility to improve the transformer's efficiency, reducing its winding and core losses, which is very hard to be accomplished in the LFTs due the innate high voltage and low frequency operational levels.

Other characteristic of the MFTs is the possibility to provide functionalities that are impossible to obtain with classical LFTs, without the inclusion of external devices. The conversion of the power-stage by power converters allows the improvement of power quality, through the power factor control, harmonics mitigations and satisfactory response under transients. Moreover, if current and voltage are controlled separately, it is possible to provide power flow control and voltage disturbance compensation (sags/flickers/swell), as additional functionalities.

On the other hand, LFT-based applications uses medium- or low-voltage power devices, as the LFT steps down the catenary voltage. Similar behavior does not occur in the SST applications since active front-end converters interface the catenary and the MFT, requiring expensive and high-voltages power devices. Moreover, the MFT designs usually use

advanced cores materials in order to achieve high efficiency levels in medium frequencies applications, increasing the cost even further. However, the cost can be compensated by the additional functionalities and improvement of either the power quality and system efficiency.

Reliability of SST-based applications should also be considered, since it tends to decrease if directly compared with LFT-based ones. In fact, the larger number of power semiconductor devices required to deal with high-voltages levels together with the complexity of the power converter structures explain such behavior. Although the SST reliability can be improved by applying redundant designs, they also increase the cost, resulting in complex design criteria. Thus, the SST-based systems are more complicated and difficult to be conceived, mostly due the number of control variables and the degree of freedom used to obtain the proper structure controllability being well greater if compared with LFT-based systems.

Table 1.1 shows the summarization of the aspects compared in SST-based application over the ones in LFT-based systems, by categorizing them as pros and cons.

PROS

Greatly reduced transformer volume and weight

High input voltage for front end converter

Higher transformer and system efficiency

Higher system cost

Better power quality

Reduced reliability

Additional functionalities

Difficult to design and manufacture

Table 1.1 – Comparison between SST-based and LFT-based applications

SOURCE: Adapted from (25).

#### 1.2.4 State-of-the-art of SST-based railway traction solutions

There are several works which present review studies and discussion in general aspects around SST, potential applications, topologies, power devices requirements, among others. Examples of such studies can be found in (13), (26), (27), (28) and (29). However, since each application of SST brings different particularities to the project, it is better to concentrate the attention in review studies focusing on railway traction systems, like the ones presented by (30) and (31). The study in (30) presents soft switching techniques applied in SST to improve the systems efficiency, while (31) presents the evolution of the individual parts of the railway traction systems, such as: power devices, transformers, drive motor systems. In (23), a deep discussion is elaborated about the MFT and six selected SST types are analyzed in the study presented by (5).

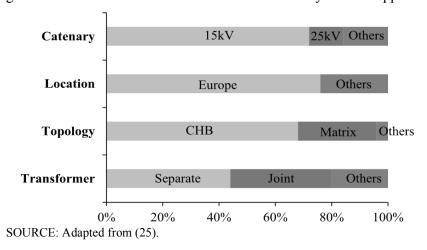

The analysis presented in (25) focus their reviews in the SST-solutions presented by both academic and industry communities. They start in the earliest concepts till the newest ones presented at the time, elaborating a series of statistic results with all the collected information.

For instance, Figure 1.4 gives the idea of how the interest in this field is mainly concentrated. It is possible to note that SST topologies for 15 kV input voltage level with cascaded structures to obtain the active front-end converter and separated MFTs processing a portion of the whole power are preferred.

Figure 1.4 – Publication statistic of SST-based railway traction application

By analyzing proposed solutions in the scientific community, it is possible to find studies lying in transformerless topologies, which are independent on transformer and based on a medium-voltage rectifier stage (32). This possibility always is limited by the semiconductor blocking-voltage capability. However, Modular Multilevel Converters (MMC) (33) has recently raised the interest in such solution due its high blocking voltage, modularity, and very high power quality. Two structures based on MMCs for transformerless traction applications are presented in (34) using either dc links or single-stage approaches. The work in (35) employs energy storage systems integrated to a MMC to recovery the kinetic energy during the braking operation using the bidirectional converter characteristic. The bidirectionality has become handy in traction applications in order to increase the efficiency of the whole vehicle electrical system.